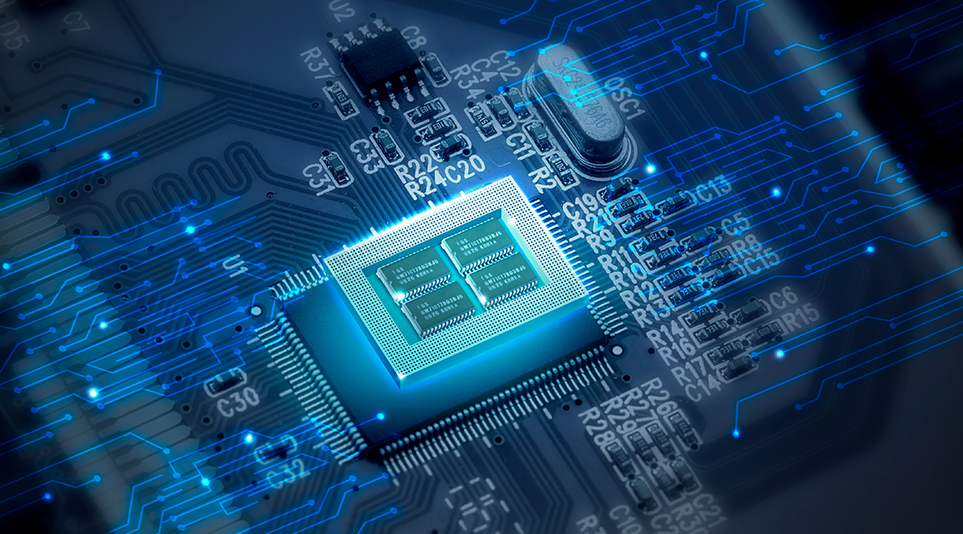

최근 등장하는 웨어러블, IoT 기기 등 혁신적인 제품의 공통점은 바로 그 중심에 두뇌 역할을 하고 있는 ‘반도체’가 있다는 점입니다. 그 중 전체 시스템을 하나의 칩으로 만들어낸 반도체 SoC(System on Chip)는 가전, 자동차, 데이터 센터 및 서버 시장 등 각 분야에서 필요로 하는 요소에 맞춰 진화하기 위해 치열한 고성능, 저전력 경쟁을 이어가고 있죠. 지난 LG 테크 콘퍼런스 2023에서 반도체 시장에 혁신을 도래할 ‘칩렛’에 대해 살펴보는 시간을 가졌습니다.

📒 NOTE

칩렛(Chiplet): 정부 공식 문서 상 ‘칩렛’으로 표준화되어, 본문 내용 또한 ‘칩렛’으로 통일하여 기입되었습니다.

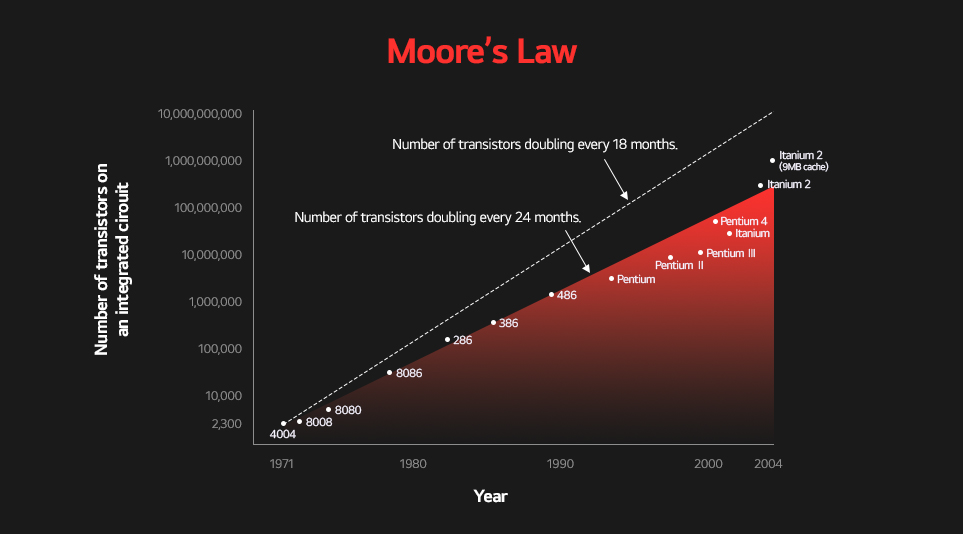

동일 면적에 집적할 수 있는 트랜지스터의 수는 2년마다 2배씩 증가해 왔는데, 우리는 이를 ‘무어의 법칙’이라고 합니다. 지난 50년간 반도체 제조 기술은 기하급수적인 발전을 이뤄오면서 이 법칙은 유효했었죠. 하지만 최근 몇 년간 “무어의 법칙이 사라졌다.” 또는 “포스트 무어 시대다”라는 말이 오르내리며 무어의 법칙이 무너져 버렸습니다. 그 이유는 직접도를 높인 공정을 새로 개발하기 위해 필요한 비용과 노력의 양이 급증하고, 웨이퍼의 가격도 치솟고 있기 때문이었죠. 이전에는 여러 개로 나누어져 있는 칩들을 하나로 통합하여 새로운 공정에서 만들면 반드시 가격경쟁력이 담보되었지만, 더 이상 그렇지 않은 시점에 도래한 것입니다.

최근에는 ‘3n(나노) 공정을 사용할 수 있는 업체는 물량이 최소 1억이 넘는 소수의 업체들뿐일 것이다’는 말이 나올 정도입니다. 최신 공정에서 칩 한 개를 개발하기 위해 초기 투입해야 하는 비용이 수천억 원 이상을 넘어섰고, 이는 업체들의 큰 진입 장벽이 되었습니다. 예를 들면, 28n 공정에서는 칩을 개발하여 천만 개를 판매하면 투자대비 수익률(ROI:Return on investment)가 나올 수 있었으나, 최신 공정에서는 수익을 거두려면 1억개보다도 더 물량이 많아야 되는 것이죠.

칩렛을 통한 반도체 산업의 혁신

칩렛(Chiplet)은 “작은 칩”이라는 뜻으로, 칩을 하나의 다이로 만들지 않고, 2개 이상으로 나누어 만드는 것을 의미합니다. 기존 MCM(Multi-chip module) 또는 SiP (System in Package)와도 유사하다고 볼 수 있지만, MCM이나 SiP는 완전히 독립적인 기능을 처리하는 여러 개의 칩을 폼팩터1)를 목적으로 하나의 패키지로 구현하는 반면, 칩렛은 하나로 만들 수 있는 것을 여러 개로 나누어서 만드는 것입니다. 패키징 기술뿐 아니라 어떻게 분리할 것인가에 해당하는 SoC 아키텍쳐가 포함되는 개념이라고 볼 수 있죠.

1) 폼팩터(Form factor): 칩의 모양 사이즈를 최종 device의 요구에 맞게 만드는 것

칩렛 적용은 반도체 개발 패러다임의 변화라고 말할 수 있는데요. 칩렛이 필요한 대표적인 3가지 이유는 다음과 같습니다.

1. 레티클 한계: 레티클(Reticle)은 반도체의 포토 공정에서 빛을 이용하여 웨이퍼 표면에 회로도를 프린트하는 틀을 의미합니다. 레티클은 크기가 26㎜x33㎜ (858㎟)로 정해져 있어, 이 크기를 넘는 칩은 반도체 공정의 특성상 만들기 매우 어렵습니다. (그래서 거의 모든 고성능 프로세서는 858㎟보다 작습니다.) 원하는 성능과 기능을 모두 포함하여 크기가 1,600㎟정도가 되어야 하는 경우, 두개의 칩으로 분리하여 패키지 내부에 통합시켜야 하며, 이러한 경우를 우리는 ‘칩렛’이라고 합니다.

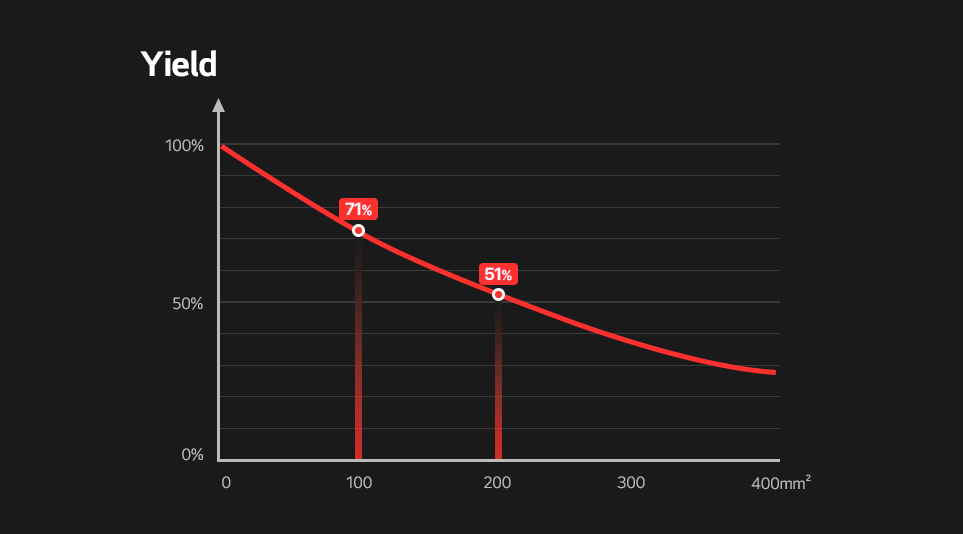

2. 수율(Yield): 반도체 제조의 수율은 면적에 반비례합니다. 위의 예시 그래프에서도 200㎟ 크기의 칩의 수율이 51%라면 400㎟ 크기의 칩의 수율은 훨씬 떨어지죠. 따라서, 패키징 내부에서의 칩-칩간 데이터 전송 구현이 가능하고, 패키징 비용의 증가를 상쇄할 수 있다면, 나누는 것이 더 경제적일 수 있습니다. 이때는 칩의 크기가 더 큰 칩을 나눌수록 경제적일 가능성이 커집니다.

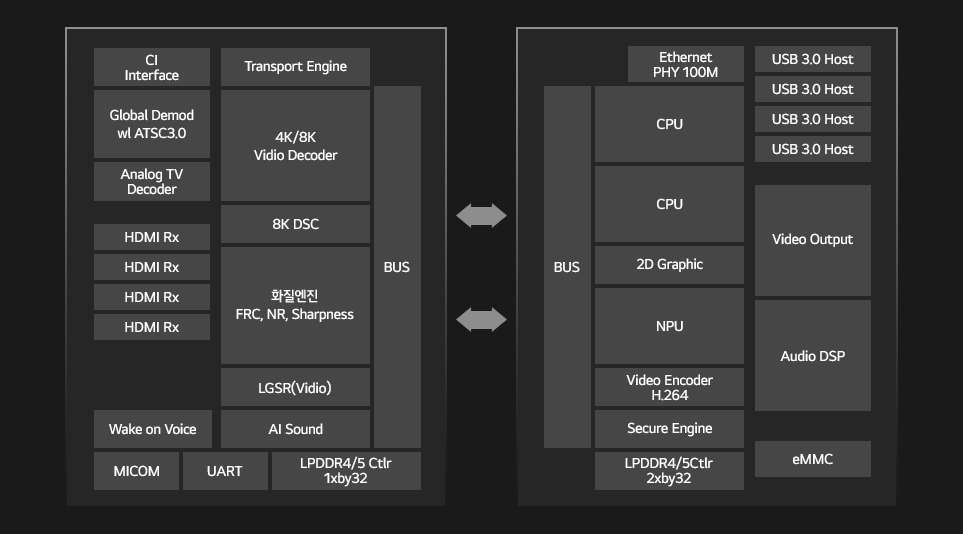

3. 재사용성과 TTM (Time-to-market)2) 그리고 성능: 칩 생산을 위해서는 수십장의 마스크3)를 만들어야 하는데 그 비용이 칩 제조에서 초기 개발비의 상당부분을 차지합니다. 새로운 노드4)가 나올 때마다 이 초기개발비는 기하급수적으로 증가하고 있죠. 또한, 고속 인터페이스인 USB 3.0, HDMI, PCIe등은 아날로그 부분의 설계가 필수적으로 포함되는데, 이러한 것들은 새로운 공정에서도 그 면적이 많이 줄어들지 않으므로, 면적 감소에 의한 가격 이익효과가 미미한 수준입니다.

2) Time-to-market: 신제품 출시하는 속도

3) 마스크: 미세한 전자회로가 그려진 유리판으로, 반도체 제조를 위한 포토 공정에서 사용.

4) 노드(node): 반도체 회로를 구성하는 트랜지스터의 선폭

하지만 기존 공정의 칩에 다이 투 다이 인터페이스를 포함시켰다면, 새로운 공정의 칩에는 고속 인터페이스를 포함시키지 않고 다이 투 다이 인터페이스만 포함시켜 제작해 기존 칩과 패키지에서 연결할 수 있습니다. 이렇게 할 경우 개발비를 급격히 줄일 수 있죠. 이 효과는 다품종 소량생산의 경우에 더 커집니다. 또한, 아키텍쳐를 잘 설계하여 A라는 칩을 N개 사용해 패키징하여 그 N배수에 근사하는 성능을 낼 수 있도록 만들 수 있다면, N배수 성능의 커다란 칩을 별도로 만들지 않아도 되겠죠. 이러한 효과를 ‘확장성’이라고 표현하며, 가격 경쟁력에 큰 도움이 됩니다. AMD의 EPYC Zen2, Zen3등도 대표적 사례죠.

SoC에 포함되는 모든 IP (Intellectual property) 블록을 독자적으로 개발하여 칩을 만드는 업체는 거의 없습니다. 많은 부분을 IP 형태로 라이선스하여 도입하고, 인하우스 차별화 IP들을 통합하여 하나의 단일 칩을 만들고 있죠. 미래에는 IP 형태의 도입도 하겠지만, 한 단계 더 나아가 칩렛들을 구매하고, 차별화 IP들이 포함된 인하우스 칩렛을 만들어 이들 여러 칩렛들을 하나로 패키징 하여 칩 제품을 개발하게 될지 모릅니다. 예를 들면 자동차용 제품을 위하여 AMD의 x86 칩렛이나 고성능 RISC-V CPU 칩렛을 구매하고, 자신의 차별화 칩렛과 통합 패키징을 하여 칩을 완성하는 것이죠.

이런 시대가 오기까지 짧게는 5년, 길게는 10년 이상 걸릴 것으로 업계는 보고 있죠. 생각보다 오랜 기간이 걸릴 것으로 예상하는 이유는 여러 업체의 칩렛을 통합하여 만들었을 때, ‘문제가 생길 경우 누가 주체가 되어서 어떻게 디버깅(debugging) 할 것인가?’, ‘책임 소재를 밝힐 수 있도록 하기 위한 테스팅 기반 기술과 방법론(testing infrastructure)이 준비되어 있는가?’ 등 여러 가지 풀어야 할 난제들이 있기 때문입니다.

이러한 문제를 풀기 위한 다방면의 연구들이 진행되고 있고, 표준화 시도도 여러 맥락에서 추진되고 있습니다. UCIe나 BoW등이 그 중 대표적인 예입니다. 또한 서로 다른 업체의 칩렛을 통합하여 하나의 칩으로 만드는 것도 시도되고 있습니다. 반도체 업계의 전설로 인정받고 있는 짐 켈러가 CEO로 있는 캐나다 AI 칩 개발사 텐스토렌트(Tenstorrent)와 LG전자와의 협력이 최근 발표됐는데요, 이 역시 이러한 차원에서 추진되고 있습니다. 대만의 시스템 반도체 업체인 MediaTek사가 NVIDIA의 GPU를 칩렛형태로 패키지에 통합하여 자동차용 제품을 개발하겠다는 발표도 있었죠. 앞서 언급한 문제들과 이에 대한 해결책들을 찾아간다면, 칩렛 기반 개발은 향후 반도체 공급 체인과 개발 생태계에 큰 변화를 일으킬 것입니다.

LG전자 SIC센터가 이끌어온 혁신

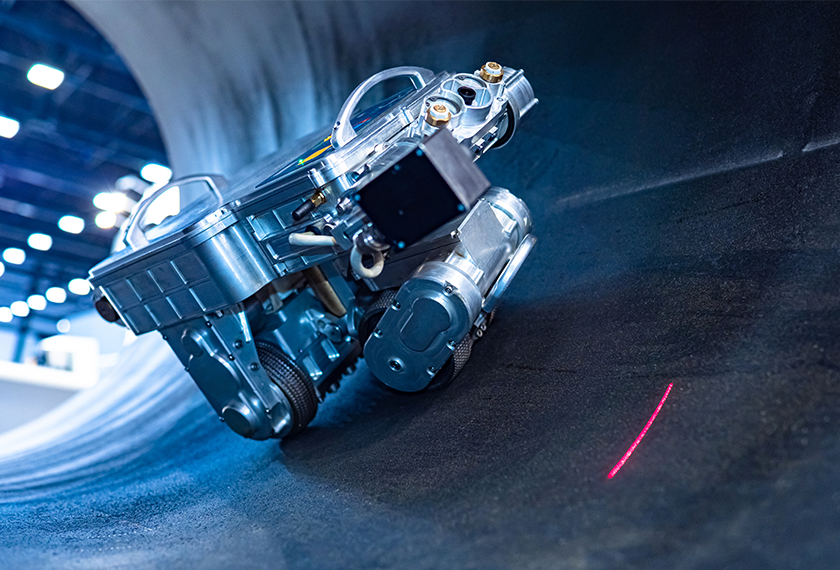

LG전자 SIC센터는 SoC설계의 전과정 및 공정 컨트롤 및 품질 관리를 담당하고 있습니다. 펩리스(Fabless) 업체로서 SIC센터에서 설계한 반도체를 TSMC와 같은 외부 파운드리 업체를 통해 위탁 생산하고 있죠.

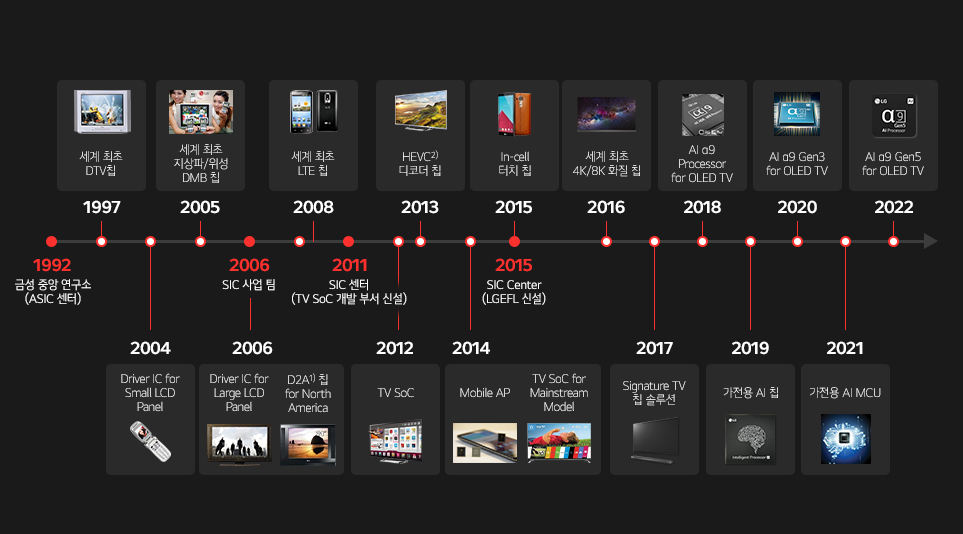

SIC센터의 모태는 1992년 설립된 금성중앙연구소 ASIC센터입니다. 이후 1997년 Digital TV 칩, 2008년 LTE 모뎀칩을 세계 최초로 개발하였습니다. 시스템 반도체 또한 지속적으로 개발하여 LG전자 프리미엄/보급형 OLED TV 및 프리미엄 가전에도 자체 개발한 칩이 적용되어 양산되고 있습니다.

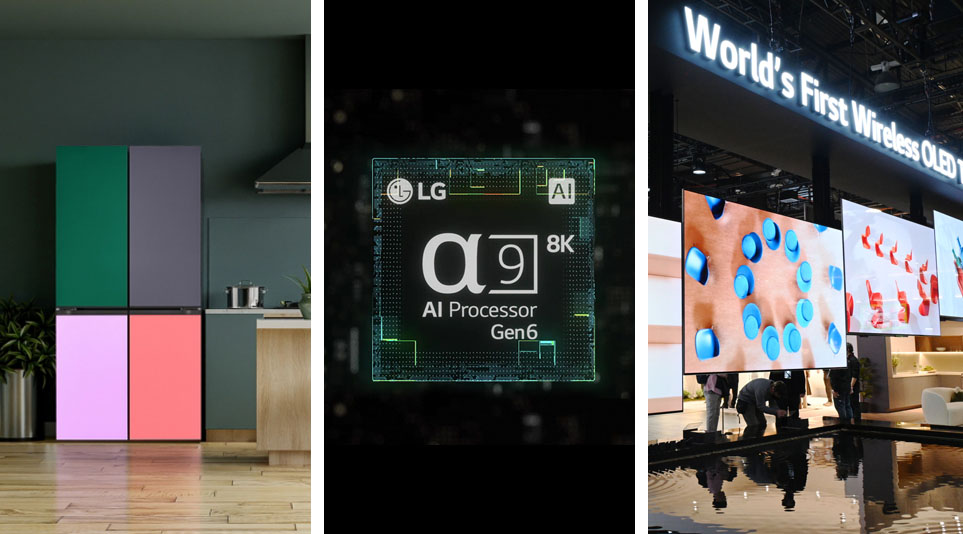

SIC센터에서 개발한 칩 중 가장 대표적인 것은 LG 올레드 TV에 적용되어 자연스러운 영상과 몰입감 넘치는 사운드를 구현하는 ‘a9(알파나인) AI 프로세서’입니다. 작년 새로 출시된 ‘LG 디오스 오브제컬렉션 무드업 냉장고’의 두뇌 역할을 하는 ‘온디바이스 AI칩’도 휴대폰을 블루투스로 연결해 음악을 재생하고 음성을 인식할 뿐 아니라 집안 분위기를 원하는 냉장고 컬러로 변경하며 취향대로 제품을 즐기는 일상을 실현했습니다. 또한 지난 1월, 세계 최대 IT·가전 박람회 CES 2023에서 공개된 ‘LG 시그니처 올레드 M’도 SIC센터에서 개발한 무선 솔루션 ‘제로 커넥트 칩셋 솔루션’을 탑재, 무선 전송 거리 최대 10미터에서 4K 120Hz 고화질 영상 및 오디오를 끊김없이 실시간으로 전송합니다. SIC 센터에서 개발한 SoC로 우리가 매일 사용하는 가전제품들을 더욱 스마트하게 만들고 고객들이 상상하지 못했던 새로운 경험을 할 수 있도록 만드는 것이 LG전자 SIC 센터가 가지고 있는 방향성과 목표입니다.

앞서 설명드린 SIC센터에서 개발한 칩들은 칩렛 기술을 적용하여 만든 것은 아직 없습니다. 하지만 향후에 개발한 칩들에는 앞에서 설명드린 이유로 칩렛의 선도적인 적용을 검토하고 있습니다.

칩렛은 사업의 종류에 따라 그 의미가 달라질 수 있습니다. 500㎟~1000㎟ 정도 크기가 되어야 하는 서버용 칩의 경우 앞에서 설명한 레티클 한계 때문에 칩렛을 적용해야 하는 상황이지만, LG전자와 같이 TV나 가전, 자동차용 등 칩의 크기가 100㎟~400㎟ 되는 경우에는 패키징 비용과 다이 투 다이 인터페이스로 인한 간접비가 상쇄되는지 확인이 필요하죠. 다품종 소량생산의 경우는 완전히 상쇄되지 않더라도, 개발비 절감, TTM 상의 이점 등으로 인해 칩렛의 적용이 유리할 수 있습니다.

이 외에 LG전자는 다양한 성능/기능의 SoC를 필요로 하는 다양한 사업을 하고 있죠. 미래의 인터렉티브 TV, 스마트 가전, 메타버스, XR 디바이스 등 떠오른 시장을 위한 선행 연구 개발을 하고 있으며, 차량용 고성능 어플리케이션을 위한 모듈 사업도 추진 중입니다. 즉, 다품종 소량 생산의 사업이죠. 이 경우 새로운 칩을 만들기 위한 초기 개발비(NRE)가 큰 장애요인이 됩니다. 하지만 칩렛 기반의 개발로 재사용이 극대화된다면, 초기 개발비 문제를 해결할 수 있으며, 궁극적으로 시장 경쟁력도 향상될 것으로 기대됩니다.